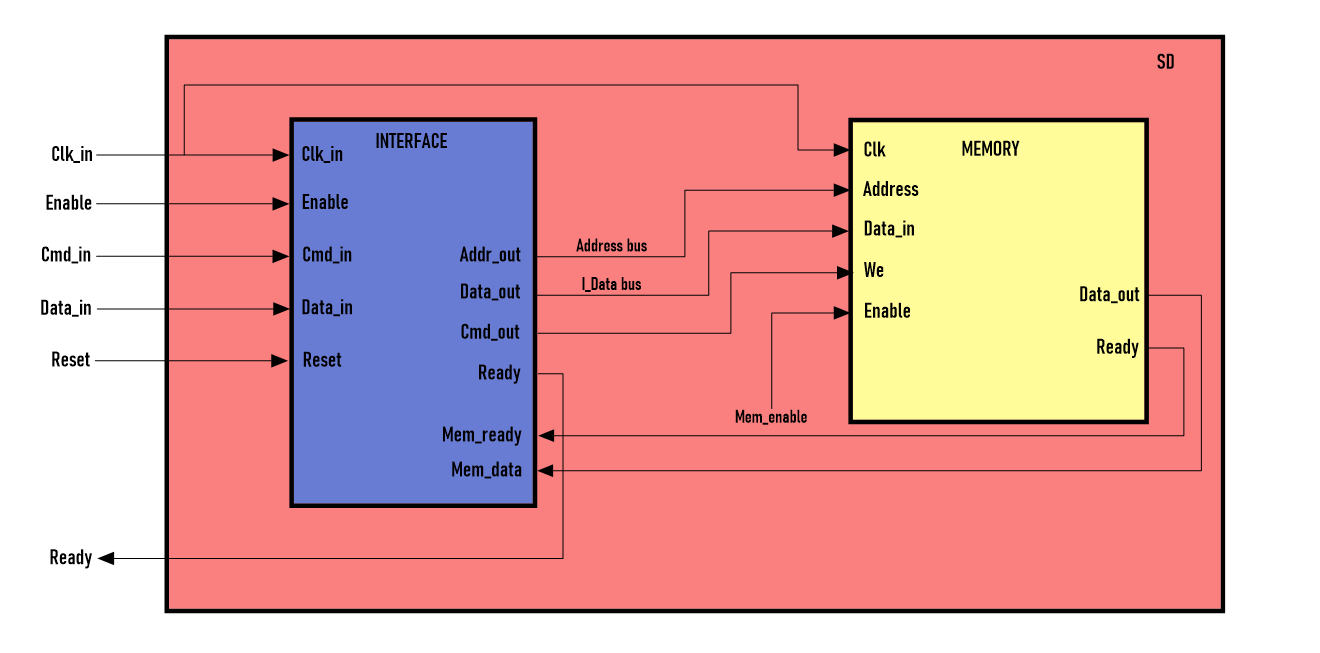

Interfaccia e memoria

L’interfaccia è il componente della scheda SD che si occupa di gestire i segnali provenienti dal master (dispositivo che monta la scheda) verso la sezione di gestione della memoria e viceversa.

Essa è composta da sei segnali che si interfacciano con il mondo esterno e sei segnali che si interfacciano con la memoria vera e propria.

Oltre ai contatti di alimentazione, i quali non sono presenti a livello di descrizione dell’hardware in VHDL, la pedinatura della scheda si compone dei seguenti segnali, tutti di tipologia std_logic e dunque segnali a singolo bit:

- clk_in : rappresenta il clock in ingresso alla scheda.

- enable: se alto, permette l’elaborazione delle informazioni ricevute sui rimanenti segnali.

- cmd_in: permette l’immissione seriale dei comandi di lettura/scrittura e abilitazione della zona nascosta. E’ dunque un segnale che può essere usato in entrambi i sensi (ingresso ed uscita) a seconda dell’operazione da eseguire.

- data: bus seriale sul quale sono presenti i bit da salvare in memoria o ottenuti dalla stessa durante una fase di lettura.

- ready: segnale che, se alto, indica la corretta terminazione di una operazione.

- reset: segnale di reset che riavvia la scheda.

Una volta inserita la scheda all’interno del dispositivo host, vengono effettuate alcune operazioni preliminari per poi entrare in una modalità di attesa di qualche comando riconosciuto:

Le tre operazioni vengono fatte in modo concorrente. La prima fase (lettura del flag per l’abilitazione della partizione nascosta) si occupa di capire se l’utilizzo della zona di memoria in oggetto è permesso o meno, andando a leggere il contenuto di una speciale cella di memoria la quale, se ad un valore logico alto, indica che la partizione nascosta della scheda SD è stata abilitata. Tale valore viene copiato in un flag interno alla scheda per un successivo utilizzo nelle fasi di lettura/scrittura e il valore della cella di memoria viene resettato di modo che, ad un successivo boot, la zona nascosta non risulti abilitata a meno di un preventivo inserimento della scheda nel dispositivo abilitante.

La seconda fase (inizializzazione della macchina a stati per la ricezione dei comandi) non fa altro che inizializzare la macchina a stati che si occupa della comprensione dei comandi impartiti dal master ad uno stato di idle, in cui attende che l’elaborazione venga abilitata alzando il valore logico del segnale enable.

L’ultima fase si occupa di capire se, al momento dell’accensione della scheda, il dispositivo master è il dispositivo abilitante. In tale occasione, una volta avvenuto il riconoscimento del dispositivo, viene forzato ad un valore alto il flag relativo all’abilitazione della regione nascosta e la scheda viene espulsa per un successivo utilizzo.

Memoria

La zona di memoria è suddivisa in due parti: la parte visibile a tutti gli utilizzatori della scheda SD e la parte nascosta, accessibile solamente dopo aver abilitato la scheda inserendola nell’apposito dispositivo abilitante. Le schede SD solitamente montano al loro interno una memoria di tipo flash non volatile. In questo progetto, tale memoria viene simulata sintetizzando un banco di memoria RAM composta da 256 parole da 32 bit l’una e la persistenza dei dati viene ottenuta effettuando un salvataggio su file di testo dell’intera memoria ad ogni operazione di scrittura. La memoria è dunque indirizzabile tramite un indirizzo a 8 bit dove i due bit più significativi possono essere forzati o meno, a seconda che si stia lavorando su una scheda la quale partizione nascosta è abilitata o meno. Uno schema generale della struttura della memoria è rappresentato dalla seguente immagine:

A livello di sintesi VHDL, il blocco rappresentante la memoria è composto da cinque segnali in ingresso e due segnali in uscita. Il segnale address è un bus a 8 bit mentre data_in è un bus a 32 bit. Una volta che la memoria ha effettuato l’operazione, ne segnala il successo ponendo ad un valore logico alto il segnale ready e immettendo i dati (in caso di lettura) sul bus data_out, anch’esso da 32 bit. Internamente, a livello di simulazione della persistenza dei dati, ad ogni scrittura viene salvato l’intero contenuto della memoria su un file di testo il quale viene importato ad ogni nuovo avvio della scheda.

Interfaccia

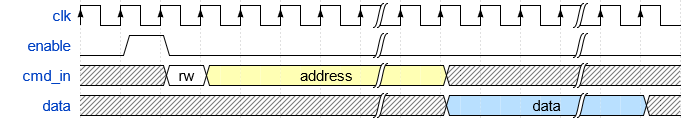

Come evidenziato in precedenza, il funzionamento dell’interfaccia e dunque dell’intero sistema, si basa su una macchina a stati che si occupa della comprensione dei comandi impartiti dal dispositivo master. Tali comandi devono dunque aderire ad un protocollo di comunicazione che descrive le informazioni da immettere sui segnali in ingresso alla scheda in relazione all’istruzione che si vuole eseguire. Il protocollo scelto implementa una versione semplificata del protocollo SPI utilizzato per l’interfaccia con memorie di tipo flash presenti nella maggior parte dei dispositivi a memorie non volatili. Esso prevede l’utilizzo di tre segnali:

- enable : viene alzato ad un valore logico alto ad indicare l’inserimento di un comando.

- cmd_in: viene usato per l’inserimento dell’istruzione da eseguire (lettura/scrittura) e dell’indirizzo di memoria alla quale tale operazione deve essere effettuata.

- data: viene usato per l’inserimento/ottenimento dei dati da scrivere/leggere in memoria all’indirizzo specificato.

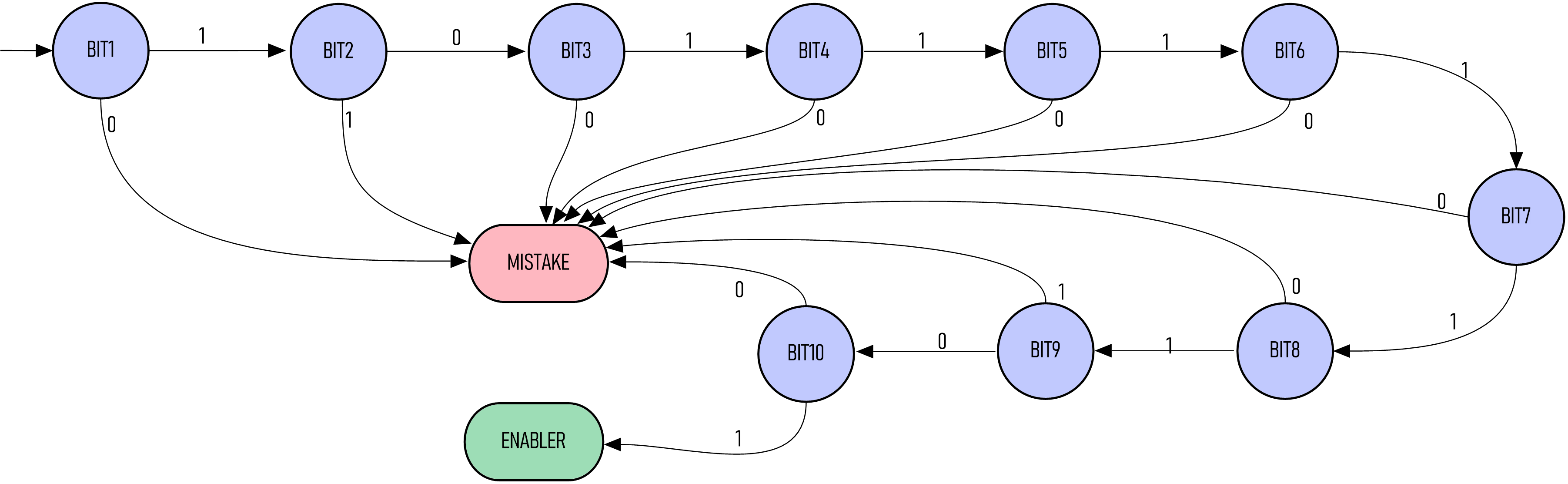

L’andamento dei segnali in questa prima fase è il seguente:

Una volta alzato il segnale enable, sul segnale cmd_in inizia la comunicazione del comando da eseguire inserendo un bit che discrimina un’operazione di lettura o scrittura, seguito dallo stream seriale dei bit rappresentanti l’indirizzo di memoria in cui leggere/scrivere dei dati. Nel caso si trattasse di una operazione di scrittura, al termine dell’inserimento dell’indirizzo in cui scrivere, sul segnale data inizia la trasmissione dei bit da salvare nella posizione indicata.

I bit rappresentanti l’indirizzo e i dati da salvare devono essere inseriti sui bus in ingresso alla memoria e dunque, l’interfaccia si occupa anche della de-serializzazione dei bit tramite un registro SIPO per fornire i dati sui bus address e data_in della memoria in modo parallelo.

Nel caso in cui il flag di accesso alla zona di memoria nascosta sia disattivato, i due bit più significativi dell’indirizzo su cui effettuare l’operazione indicata vengono forzati a 0 prima di inserirli sul bus opportuno della memoria, in modo da obbligare il dispositivo a lavorare esclusivamente nella partizione libera senza alcuna possibilità di intervenire sull’indirizzo. L’utilizzatore non si accorgerà di nulla in quanto l’operazione verrà portata a buon fine su un indirizzo diverso da quello specificato, come è possibile notare dalla seguente immagine. Infatti, l’utilizzatore della scheda effettua una richiesta di scrittura con successiva lettura allo stesso indirizzo, il quale appartiene alla zona di memoria nascosta. Tale indirizzo viene dunque modificato ma, a monte della scheda, l’operazione sembra essere comunque stata effettuata all’indirizzo specificato.

Nel caso di una lettura, la memoria fornirà sul suo bus data_out la stringa di 32 bit presente all’indirizzo indicato. Dunque, l’interfaccia si occupa anche della serializzazione dei dati provenienti dalla memoria tramite un registro PISO per porli poi in uscita sul segnale data. L’utilizzatore della scheda dovrà dunque utilizzare quest’ultimo segnale sia come ingresso (per inserire i dati da scrivere ad un determinato indirizzo) sia come uscita (per leggere i dati ritrovati all’indirizzo specificato).

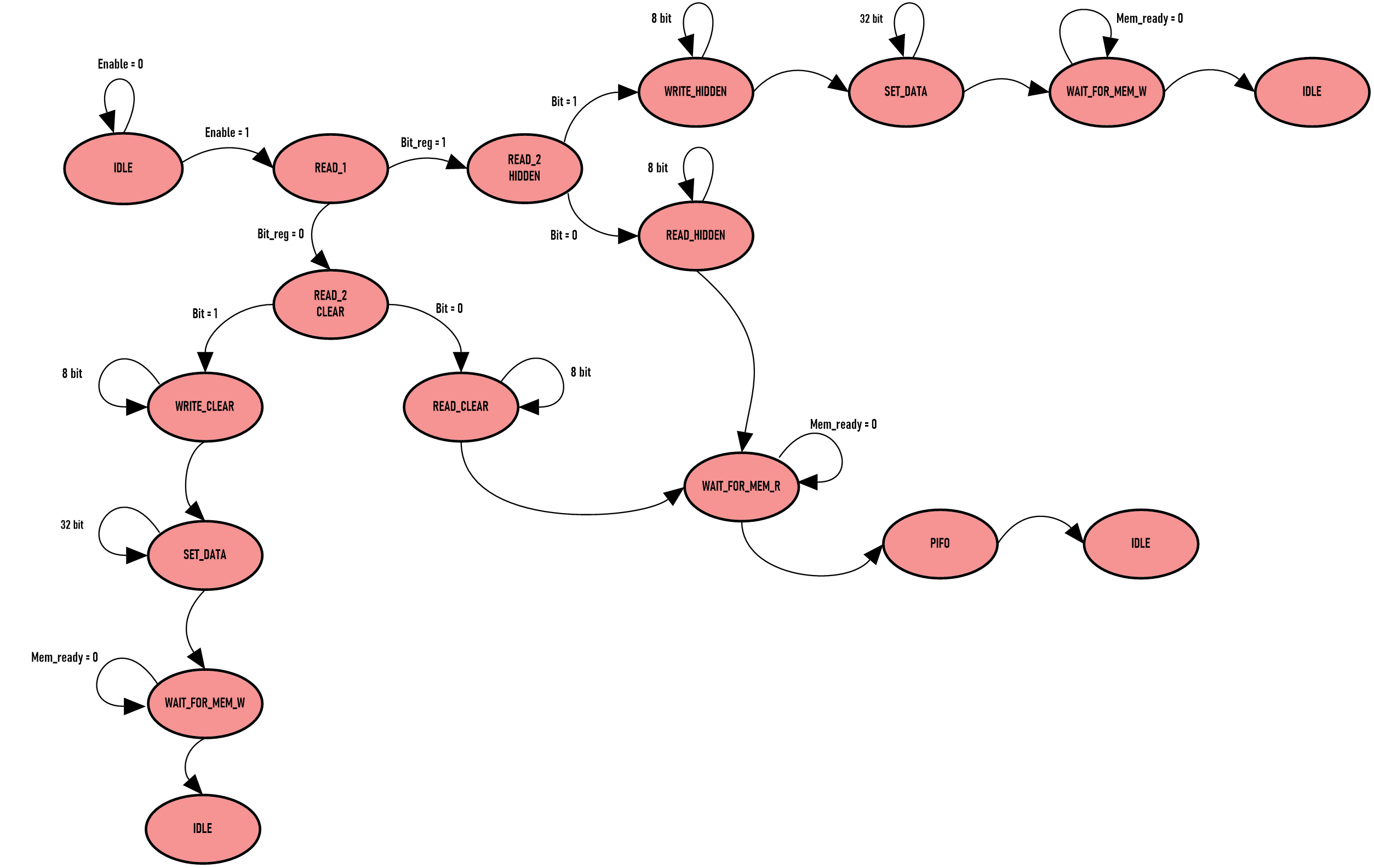

Tutte queste operazioni vengono descritte tramite una macchina a stati il quale diagramma di transizione è visualizzabile nella seguente figura:

E’ composta da 17 stati e la radice è lo stato di IDLE, nel quale il dispositivo rimane in congelamento nell’attesa che una operazione venga specificata. Appena il segnale enable diventa alto, l’elaborazione ha inizio. Ogni stato effettua delle precise operazioni. La prima parte di transizioni si concentra nel discriminare il comando impartito (lettura o scrittura) e la lettura del flag di abilitazione della memoria per capire se è necessario oscurare la partizione nascosta o renderla fisicamente indirizzabile. La seguente tabella dimostra la discriminazione dell’istruzione a seconda del valore dei segnali interessati:

| reg_enable |

cmd_in (r/w) |

azione da eseguire |

stato di arrivo |

| 1 |

1 |

Scrittura con zona proibita abilitata |

WRITE_HIDDEN |

| 1 |

0 |

Lettura con zona proibita abilitata

|

READ_HIDDEN |

| 0 |

1 |

Scrittura con zona proibita NON abilitata |

WRITE_CLEAR |

| 0 |

0 |

Lettura con zona proibita NON abilitata |

READ_CLEAR |

Negli stati di arrivo, viene letto l’indirizzo al quale effettuare l’azione indicata e viene posto su un segnale a 8 bit che si interfaccia con la memoria. Nel caso di scritture, si passa allo stato SET_DATA il quale si occupa di leggere i 32 bit dei dati da scrivere in memoria e disporli su un bus della stessa lunghezza. A questo punto, la transizione prosegue nello stato WAIT_FOR_MEMORY_W dove viene abilitata la memoria per l’esecuzione dell’operazione. L’interfaccia rimane in attesa della corretta scrittura da parte della memoria ascoltando il relativo segnale di ready. Una volta che tale segnale diventa alto, la memoria ha terminato l’operazione e l’interfaccia si pone nuovamente nello stato di IDLE in attesa di una successiva operazione. Nel caso di letture invece, dagli stati specificati in tabella si giunge nello stato WAIT_FOR_MEM_R nel quale si attende che la memoria finisca l’operazione di lettura e fornisca i dati sul suo bus di uscita. A questo punto si passa allo stato PISO il quale si occupa di serializzare i dati arrivati dalla memoria e porli, un bit alla volta, sul pin data della scheda. Alla fine di questa operazione, la macchina a stati converge nello stato IDLE.

SD.vhd

SD.vhd